#### **Hardware Performance Counters**

- AMD Opteron Hardware Performance Counters

- Four 48-bit performance counters.

- > Each counter can monitor a single event

- Count specific processor events

- » the processor increments the counter when it detects an occurrence of the event

- » (e.g., cache misses)

- Duration of events

- » the processor counts the number of processor clocks it takes to complete an event

- » (e.g., the number of clocks it takes to return data from memory after a cache miss)

- Time Stamp Counters (TSC)

- > Cycles (user time)

September 21-24, 2009

Luiz DeRose (Idr@cray.com) © Cray Inc

3

#### **PAPI Predefined Events**

- Common set of events deemed relevant and useful for application performance tuning

- Accesses to the memory hierarchy, cycle and instruction counts, functional units, pipeline status, etc.

- The "papi\_avail" utility shows which predefined events are available on the system execute on compute node

- PAPI also provides access to native events

- The "papi\_native\_avail" utility lists all AMD native events available on the system – execute on compute node

- Information on PAPI and AMD native events

- pat\_help counters

- man papi\_counters

- For more information on AMD counters:

- > http://www.amd.com/us-en/assets/content\_type/white\_papers\_and\_tech\_docs/26049.PDF

September 21-24, 2009

Luiz DeRose (ldr@cray.com) © Cray Inc

4

#### **Hardware Counters Selection**

- PAT\_RT\_HWPC <set number> | <event list>

- · Specifies hardware counter events to be monitored

- A set number can be used to select a group of predefined hardware counters events (recommended)

- o CrayPat provides 19 groups on the Cray XT systems

- Alternatively a list of hardware performance counter event names can be used

- Maximum of 4 events

- Both formats can be specified at the same time, with later definitions overriding previous definitions

- > Hardware counter events are not collected by default

- Hardware counters collection is not supported with sampling on systems running Catamount on the compute nodes

September 21-24, 2009

Luiz DeRose (ldr@cray.com) © Cray Inc.

\_

#### **Accuracy Issues**

- Granularity of the measured code

- If not sufficiently large enough, overhead of the counter interfaces may dominate

- Pay attention to what is not measured:

- Out-of-order processors

- Speculation

- · Lack of standard on what is counted

- > Microbenchmarks can help determine accuracy of the hardware counters

- For more information on AMD counters:

- · architecture manuals:

- > http://www.amd.com/us-en/assets/content\_type/white\_papers\_and\_tech\_docs/26049.PDF

September 21-24, 2009

Luiz DeRose (ldr@cray.com) © Cray Inc.

6

#### CRAY **Hardware Performance Counters** Hardware performance counter events: PAPI\_L1\_DCM Level 1 data cache misses CYCLES\_RTC User Cycles (approx, from rtc) PAPI\_TLB\_DM Data translation lookaside buffer misses PAPI\_FP\_OPS Floating point operations Estimated minimum overhead per call of a traced function, which was subtracted from the data shown in this report (for raw data, use the option: -s overhead=include): PAPI\_L1\_DCM PAPI\_TLB\_DM 8.040 misses 0.005 misses PAPI\_L1\_DCA 474.080 refs PAPI\_FP\_OPS 0.000 ops CYCLES RTC 1863.680 cycles 0.693 microseconds Time September 21-24, 2009 Luiz DeRose (Idr@cray.com) © Cray Inc.

```

PAT RT HWPC=0 (Summary with Instructions)

PAPI_TOT_INS Instructions count

PAPI_L1_DCA Level 1 data cache accesses

PAPI_FP_OPS

PAPI_L1_DCM

Floating point operations

Data Cache Miss

User_Cycles Virtual Cycles

USER

Time%

98.6%

4.442352 secs

Imb.Time

-- secs

Tmb. Time%

0.001M/sec

4500.0 calls

Calls

PAPI_L1_DCM

PAPI_TOT_INS

14.807M/sec

530.210M/sec

65771688 misses

2355221562 instr

PAPI_L1_DCA

PAPI_FP_OPS

332.718M/sec

1477953890 refs

44.765M/sec 1975672594 ops

4.442 secs 11993557493 cycles 100.0%Time

444.765M/sec

User time (approx)

Average Time per Call

CrayPat Overhead : Time

0.000987 sec

0.1%

HW FP Ops / User time

HW FP Ops / WCT

HW FP Ops / Inst

1975672594 ops 4.1%peak(DP)

444.765M/sec

444.736M/sec

83.9%

1.34 ops/ref

Computational intensity

0.16 ops/cycle

Instr per cycle

0.20 inst/cycle

2120.84M/sec

MFLOPS (aggregate)

1779.06M/sec

Instructions per LD & ST 62.8% refs

D1 cache hit,miss ratios 95.5% hits

D1 cache utilization (misses) 22.47 refs/miss

1.59 inst/ref

4.5% misses

2.809 avg hits

______

September 21-24, 2009

Luiz DeRose (ldr@cray.com) © Cray Inc.

```

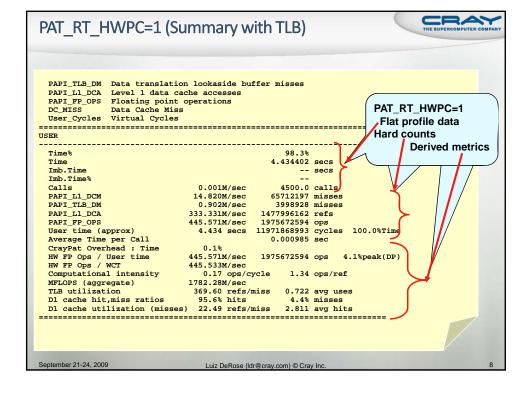

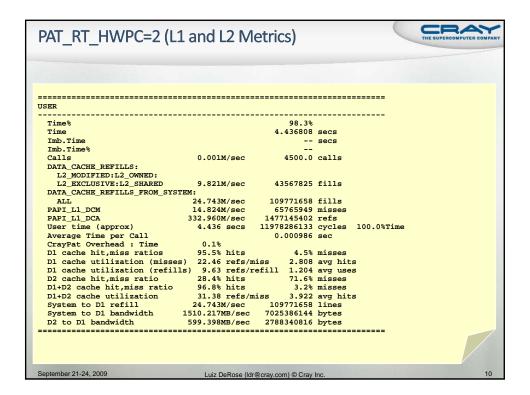

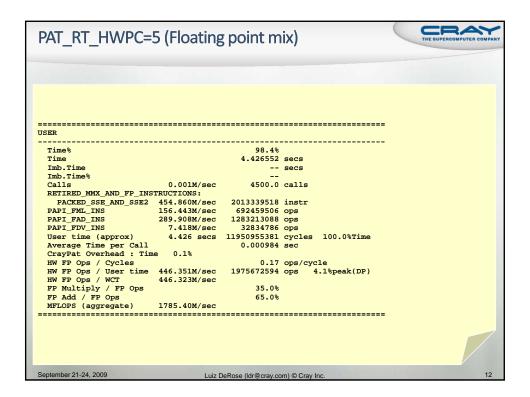

## How do I interpret these derived metrics?

- The following thresholds are guidelines to identify if optimization is needed:

- Computational Intensity: < 0.5 ops/ref

- > This is the ratio of FLOPS by L&S

- > Measures how well the floating point unit is being used

- FP Multiply / FP Ops or FP Add / FP Ops: < 25%

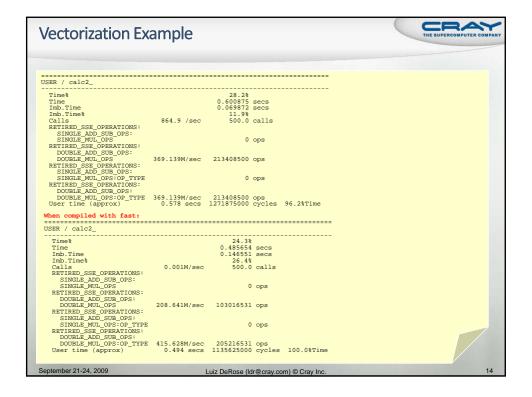

- Vectorization: < 1.5

September 21-24, 2009

Luiz DeRose (Idr@cray.com) © Cray Inc.

15

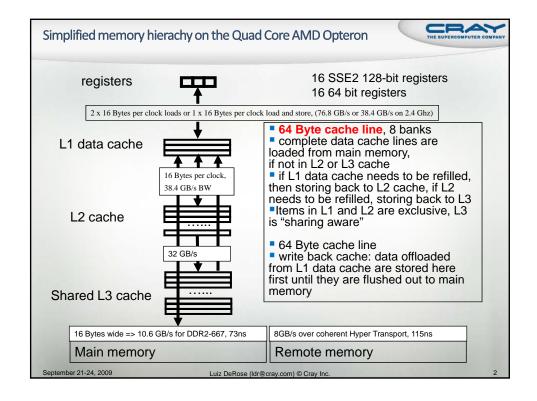

## **Memory Hierarchy Thresholds**

- TLB utilization: < 90.0%</li>

- Measures how well the memory hierarchy is being utilized with regards to TLB

- This metric depends on the computation being single precision or double precision

- A page has 4 Kbytes. So, one page fits 512 double precision words or 1024 single precision words

- TLB utilization < 1 indicates that not all entries on the page are being utilized between two TLB misses

- D1 cache utilization: < 1 (D1+D2 cache utilization: < 1)</p>

- A cache line has 64 bytes (8 double precision words or 16 single precision words)

- D1 cache utilization < 1 indicates that not all entries on the cache line are being utilized between two cache misses

- D1 cache hit (or miss) ratios: < 90% ( > 10%)

- D2 (L2) cache hit (or miss) ratios: < 95% ( > 5%)

- D1 + D2 cache hit (or miss) ratios: < 92% ( > 8%)

- D1 and D2 caches on the Opteron are complementary

- This metric provides a view of the Total Cache hit (miss) ratio

September 21-24, 2009

Luiz DeRose (ldr@cray.com) © Cray Inc

16

# Using Hardware Performance Counters

# Questions / Comments Thank You!

CSC, Finland

Luiz DeRose (Idr@cray.com) © Cray In

September 21-24, 2009